by Kevin

Starting from Scratch

I was minding my own business when my project lead Jan approached me with a new assignment. At the time, General Dynamics in Scottsdale had hundreds of engineers working on the new MUOS satellite constellation. They needed some FPGA design on the User-to-Base data link.

I agreed, and found myself confronted with a VME chassis. One slot held an embedded processor card. Another held a card with 6 Virtex-II FPGA's. There was nothing else in the chassis. Also, there was nobody else on the project.

Step Up to the Plate

We were chronically understaffed. Promised help never arrived. I took on the entire FPGA design, which demodulated and downsampled RF data directly from the tuner. My design quickly grew to encompass 5 of the 6 available FPGA's.

Once again, this was life on the leading edge: sampling and data rates that stretched the capabilities of the available processors. I used one entire FPGA on the first decimation stage, a Hogenauer filter written as parallel shift and addition stages to meet timing. I snaked high-speed parallel data among the FPGA's using a fresh-to-market interface called "Rocket I/O." I did it blindfolded with one hand tied behind my back.*

The Inner MacGyver

One of the managers had put his fingers on the design. He specified a "free" embedded Linux system for the controller card and left just before I arrived. I looked it up and discovered it was a) not free, b) an evaluation-only copy, and c) $35,000 to license per seat per year.

We were left with no embedded Linux, but we had a darned resourceful engineer on the case. I scoured the internet and cobbled together:

- Fresh kernel source from the latest release

- A kernel configuration file from some guy's server in Italy

- An open-source root filesystem from Germany

- A gcc cross-compiler from God-knows-where

Quite a lash-up, but it booted and ran all the drivers for the FPGA card. Jan almost fainted when I explained what I had done, but he nodded and wandered off in a daze to smooth things with the import controls people...

Can't Argue With Success

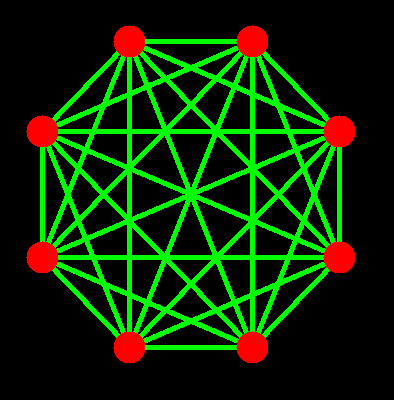

Eventually I got some software help and we brought it all up in the lab. After some fine-tuning, the system produced a gorgeous 8PSK constellation plot on the vector signal analyzer display. It really did look like the image to the left.

And then the next satellite launch exploded, the program was suspended for two years and we all got laid off.

*Because of the clumsy graphical toolset forced on us by management... Let's not go there.