by Kevin

A Bold New Design

In 2018, North Star Scientific, located in Kapolei on the island of O`ahu, was awarded a contract to develop the transmit/

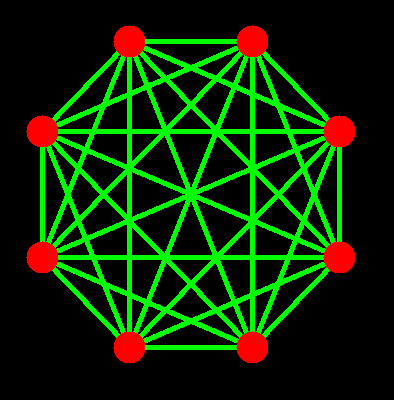

Such a thing did not exist. Circular arrays certainly did, and planar phased arrays running to hundreds of elements, but we couldn't find any examples that operated at high power.

This was an ambitious project for North Star. They were mostly an antenna house, and they had built a few amplifiers and such, but nothing like a high-frequency radar transducer operating with insane precision.

Demanding Requirements

If you know anything about phased arrays, you know that timing errors of a tiny fraction can wipe out your radar beams and destroy your performance. At the frequencies we were running, these fractions amounted to a handful of picoseconds.

Each element in the array brought its own stringent requirements:

- Dedicated digitizers operating at gigasamples per second

- Gigabytes of memory for pulse capture and post-processing

- A timing network that provided sampling clocks and trigger pulses with picosecond precision

- A network connection capable of offloading received samples at high speed

And there were to be hundreds of elements.

"Through The Power Of Math"

There was no way to brute-force the requirements in an FPGA with ever-higher clock rates, for example; as the local mathematician, I introduced custom Farrow filters to precisely adjust the signal timing, along with such exotica as Cartesian linearization loops and narrow-band interference excision in the frequency domain.

There was plenty of rigor demanded of my FPGA designs in any case. The wonders of the JESD-204b specification were mine to explore, along with interfaces to DDR-4 memory and PCI(e) buses, and lots and lots of signal processing.

A Song of Clocks and Drivers

We built several custom boards through the course of the project, and I assisted with the PCB design. In addition to FPGA pin placement and I/O formats, I did schematic design for several peripherals and assisted the layout and modelling teams.

All of this had to be troubleshot and brought up in the lab. I had special fun with a clock distribution card that didn't distribute any clocks. I was able to bring it up by cutting and wiring over traces, swapping resistors and changing driver chips. Hey, it worked!

Meanwhile, In the Lab

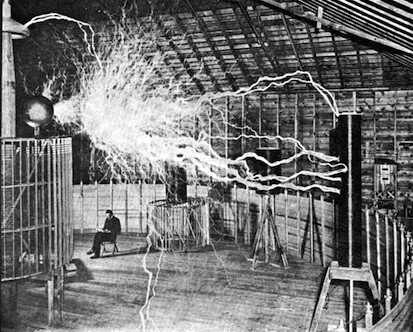

While I labored over FPGA designs and circuit traces, the other engineers were firing up high-powered (and expensive!) RF amplifiers and blasting coolant through aluminum mounting plates. High voltage, ear protection and embedded software debugging: just another day at North Star Scientific!

In the end, we demonstrated a prototype that operated at full power, generating and receiving radar chirps aligned within less than 100 picoseconds. It was a brilliant technical success, one that all of us can be proud of.